openMSP430

openMSP430

Project maintainers

Details

Created: Jun 30, 2009

Updated: Mar 21, 2021

SVN Updated: Apr 8, 2018

SVN: Browse

Latest version: download (might take a bit to start...)

Statistics: View

Bugs: 40 reported / 37 solved

Other project properties

Language:Verilog

Development status:Stable

Additional info:ASIC proven, Design done, FPGA proven, Specification done

WishBone compliant: No

WishBone version: n/a

License: BSD

Introduction

The openMSP430 is a synthesizable 16bit microcontroller core written in Verilog. It is compatible with Texas Instruments' MSP430 microcontroller family and can execute the code generated by any MSP430 toolchain in a near cycle accurate way.

The core comes with some peripherals (16x16 Hardware Multiplier, Watchdog, GPIO, TimerA, generic templates), with a DMA interface, and most notably with a two-wire Serial Debug Interface supporting the MSPGCC GNU Debugger (GDB) for in-system software debugging.

While being fully FPGA friendly, this design is also particularly suited for ASIC implementations (typically mixed signal ICs with strong area and low-power requirements).

In a nutshell, the openMSP430 brings with it:

- Low area (8k-Gates), without hidden extra infrastructure overhead (memory backbone, IRQ controller and watchdog timer are already included).

- Excellent code density.

- Good performances.

- Build-in power and clock managment options.

- Multiple times Silicon Proven.

Download

Design

The complete tar archive of the project can be downloaded here (OpenCores account required).

The following SVN command can be run from a console (or GUI):

svn export http://opencores.org/ocsvn/openmsp430/openmsp430/trunk/ openmsp430

ChangeLog

- The Core's ChangeLog lists the CPU updates.

- The Tools' ChangeLog lists the Software development tools updates.

Subscribe to the following RSS feed to keep yourself informed about ALL updates.

Documentation

Being fully compatible with the original MSP430 architecture, TI's official documentation is applicable: SLAU049F.PDF

In addition, the openMSP430 online documentation is also available in pdf.

Features & Limitations

Features

Core:

- Full instruction set support.

- Interrupts: IRQs (x14, x30 or x62), NMI (x1).

- Low Power Modes (LPMx).

- Configurable memory size for both program and data.

- Scalable peripheral address space.

- DMA interface.

- Two-wire Serial Debug Interface (I2C or UART based) with GDB support (Nexus class 3, w/o trace).

- FPGA friendly (option for single clock domain, no clock gate).

ASIC friendly (options for full power & clock management support).

Small size (Xilinx: 1650 LUTs / Altera: 1550 LEs / ASIC: 8k gates).

Peripherals:

- 16x16 Hardware Multiplier.

- Basic Clock Module.

- Watchdog.

- Timer A (FPGA only).

- GPIOs (FPGA only).

- Templates for 8 and 16 bit peripherals.

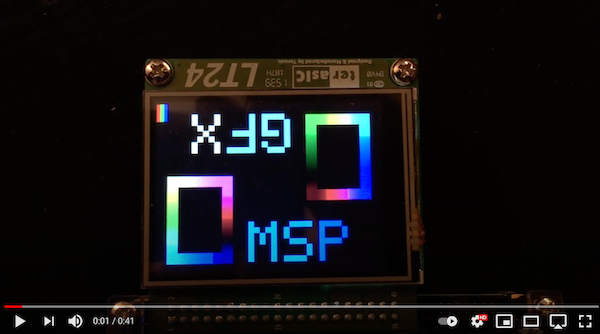

- Graphic Controller (openGFX430)

Limitations

Core:

- Instructions can't be executed from the data memory.

Links

Follow on Google+:

Discussion group:

Subscribe to openMSP430

Email:

Development has been performed using the following freely available (excellent) tools:

- Icarus Verilog : Verilog simulator.

- GTKWave Analyzer : Waveform viewer.

- MSPGCC : GCC toolchain for the Texas Instruments MSP430 MCUs.

- ISE WebPACK : Xilinx's free FPGA synthesis tool.

A few MSP430 links:

- Wikipedia: MSP430

- TI: MSP430x1xx Family User's Guide

TI: a list of available MSP430 Open Source projects out there on the web today.

Legal information

MSP430 is a trademark of Texas Instruments, Inc. This project is not affiliated in any way with Texas Instruments. All other product names are trademarks or registered trademarks of their respective owners.